|

|

|

MSP432E4 DriverLib API Guide

1.11.00.03

|

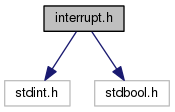

#include <stdint.h>#include <stdbool.h>

Go to the source code of this file.

Macros | |

| #define | FAULT_NMI 2 |

| #define | FAULT_HARD 3 |

| #define | FAULT_MPU 4 |

| #define | FAULT_BUS 5 |

| #define | FAULT_USAGE 6 |

| #define | FAULT_SVCALL 11 |

| #define | FAULT_DEBUG 12 |

| #define | FAULT_PENDSV 14 |

| #define | FAULT_SYSTICK 15 |

| #define | INT_GPIOA 16 |

| #define | INT_GPIOB 17 |

| #define | INT_GPIOC 18 |

| #define | INT_GPIOD 19 |

| #define | INT_GPIOE 20 |

| #define | INT_UART0 21 |

| #define | INT_UART1 22 |

| #define | INT_SSI0 23 |

| #define | INT_I2C0 24 |

| #define | INT_PWM0_FAULT 25 |

| #define | INT_PWM0_0 26 |

| #define | INT_PWM0_1 27 |

| #define | INT_PWM0_2 28 |

| #define | INT_QEI0 29 |

| #define | INT_ADC0SS0 30 |

| #define | INT_ADC0SS1 31 |

| #define | INT_ADC0SS2 32 |

| #define | INT_ADC0SS3 33 |

| #define | INT_WATCHDOG 34 |

| #define | INT_TIMER0A 35 |

| #define | INT_TIMER0B 36 |

| #define | INT_TIMER1A 37 |

| #define | INT_TIMER1B 38 |

| #define | INT_TIMER2A 39 |

| #define | INT_TIMER2B 40 |

| #define | INT_COMP0 41 |

| #define | INT_COMP1 42 |

| #define | INT_COMP2 43 |

| #define | INT_SYSCTL 44 |

| #define | INT_FLASH 45 |

| #define | INT_GPIOF 46 |

| #define | INT_GPIOG 47 |

| #define | INT_GPIOH 48 |

| #define | INT_UART2 49 |

| #define | INT_SSI1 50 |

| #define | INT_TIMER3A 51 |

| #define | INT_TIMER3B 52 |

| #define | INT_I2C1 53 |

| #define | INT_CAN0 54 |

| #define | INT_CAN1 55 |

| #define | INT_EMAC0 56 |

| #define | INT_HIBERNATE 57 |

| #define | INT_USB0 58 |

| #define | INT_PWM0_3 59 |

| #define | INT_UDMA 60 |

| #define | INT_UDMAERR 61 |

| #define | INT_ADC1SS0 62 |

| #define | INT_ADC1SS1 63 |

| #define | INT_ADC1SS2 64 |

| #define | INT_ADC1SS3 65 |

| #define | INT_EPI0 66 |

| #define | INT_GPIOJ 67 |

| #define | INT_GPIOK 68 |

| #define | INT_GPIOL 69 |

| #define | INT_SSI2 70 |

| #define | INT_SSI3 71 |

| #define | INT_UART3 72 |

| #define | INT_UART4 73 |

| #define | INT_UART5 74 |

| #define | INT_UART6 75 |

| #define | INT_UART7 76 |

| #define | INT_I2C2 77 |

| #define | INT_I2C3 78 |

| #define | INT_TIMER4A 79 |

| #define | INT_TIMER4B 80 |

| #define | INT_TIMER5A 81 |

| #define | INT_TIMER5B 82 |

| #define | INT_SYSEXC 83 |

| #define | INT_I2C4 86 |

| #define | INT_I2C5 87 |

| #define | INT_GPIOM 88 |

| #define | INT_GPION 89 |

| #define | INT_TAMPER0 91 |

| #define | INT_GPIOP0 92 |

| #define | INT_GPIOP1 93 |

| #define | INT_GPIOP2 94 |

| #define | INT_GPIOP3 95 |

| #define | INT_GPIOP4 96 |

| #define | INT_GPIOP5 97 |

| #define | INT_GPIOP6 98 |

| #define | INT_GPIOP7 99 |

| #define | INT_GPIOQ0 100 |

| #define | INT_GPIOQ1 101 |

| #define | INT_GPIOQ2 102 |

| #define | INT_GPIOQ3 103 |

| #define | INT_GPIOQ4 104 |

| #define | INT_GPIOQ5 105 |

| #define | INT_GPIOQ6 106 |

| #define | INT_GPIOQ7 107 |

| #define | INT_GPIOR 108 |

| #define | INT_GPIOS 109 |

| #define | INT_SHA0 110 |

| #define | INT_AES0 111 |

| #define | INT_DES0 112 |

| #define | INT_LCD0 113 |

| #define | INT_TIMER6A 114 |

| #define | INT_TIMER6B 115 |

| #define | INT_TIMER7A 116 |

| #define | INT_TIMER7B 117 |

| #define | INT_I2C6 118 |

| #define | INT_I2C7 119 |

| #define | INT_ONEWIRE0 121 |

| #define | INT_I2C8 125 |

| #define | INT_I2C9 126 |

| #define | INT_GPIOT 127 |

| #define | NUM_INTERRUPTS 129 |

| #define | NUM_PRIORITY 8 |

| #define | NUM_PRIORITY_BITS 3 |

| #define | INT_PRIORITY_MASK ((0xFF << (8 - NUM_PRIORITY_BITS)) & 0xFF) |

Functions | |

| bool | IntMasterEnable (void) |

| bool | IntMasterDisable (void) |

| void | IntRegister (uint32_t ui32Interrupt, void(*pfnHandler)(void)) |

| void | IntUnregister (uint32_t ui32Interrupt) |

| void | IntPriorityGroupingSet (uint32_t ui32Bits) |

| uint32_t | IntPriorityGroupingGet (void) |

| void | IntPrioritySet (uint32_t ui32Interrupt, uint8_t ui8Priority) |

| int32_t | IntPriorityGet (uint32_t ui32Interrupt) |

| void | IntEnable (uint32_t ui32Interrupt) |

| void | IntDisable (uint32_t ui32Interrupt) |

| uint32_t | IntIsEnabled (uint32_t ui32Interrupt) |

| void | IntPendSet (uint32_t ui32Interrupt) |

| void | IntPendClear (uint32_t ui32Interrupt) |

| void | IntPriorityMaskSet (uint32_t ui32PriorityMask) |

| uint32_t | IntPriorityMaskGet (void) |

| void | IntTrigger (uint32_t ui32Interrupt) |

| #define FAULT_NMI 2 |

Referenced by IntPendSet().

| #define FAULT_HARD 3 |

| #define FAULT_MPU 4 |

Referenced by IntDisable(), IntEnable(), IntIsEnabled(), MPUIntRegister(), and MPUIntUnregister().

| #define FAULT_BUS 5 |

Referenced by IntDisable(), IntEnable(), and IntIsEnabled().

| #define FAULT_USAGE 6 |

Referenced by IntDisable(), IntEnable(), and IntIsEnabled().

| #define FAULT_SVCALL 11 |

| #define FAULT_DEBUG 12 |

| #define FAULT_PENDSV 14 |

Referenced by IntPendClear(), and IntPendSet().

| #define FAULT_SYSTICK 15 |

Referenced by IntDisable(), IntEnable(), IntIsEnabled(), IntPendClear(), IntPendSet(), SysTickIntRegister(), and SysTickIntUnregister().

| #define INT_GPIOA 16 |

| #define INT_GPIOB 17 |

| #define INT_GPIOC 18 |

| #define INT_GPIOD 19 |

| #define INT_GPIOE 20 |

| #define INT_UART0 21 |

| #define INT_UART1 22 |

| #define INT_SSI0 23 |

| #define INT_I2C0 24 |

| #define INT_PWM0_FAULT 25 |

| #define INT_PWM0_0 26 |

| #define INT_PWM0_1 27 |

| #define INT_PWM0_2 28 |

| #define INT_QEI0 29 |

| #define INT_ADC0SS0 30 |

| #define INT_ADC0SS1 31 |

| #define INT_ADC0SS2 32 |

| #define INT_ADC0SS3 33 |

| #define INT_WATCHDOG 34 |

Referenced by WatchdogIntRegister(), and WatchdogIntUnregister().

| #define INT_TIMER0A 35 |

| #define INT_TIMER0B 36 |

| #define INT_TIMER1A 37 |

| #define INT_TIMER1B 38 |

| #define INT_TIMER2A 39 |

| #define INT_TIMER2B 40 |

| #define INT_COMP0 41 |

Referenced by ComparatorIntRegister(), and ComparatorIntUnregister().

| #define INT_COMP1 42 |

| #define INT_COMP2 43 |

| #define INT_SYSCTL 44 |

Referenced by SysCtlIntRegister(), and SysCtlIntUnregister().

| #define INT_FLASH 45 |

Referenced by FlashIntRegister(), and FlashIntUnregister().

| #define INT_GPIOF 46 |

| #define INT_GPIOG 47 |

| #define INT_GPIOH 48 |

| #define INT_UART2 49 |

| #define INT_SSI1 50 |

| #define INT_TIMER3A 51 |

| #define INT_TIMER3B 52 |

| #define INT_I2C1 53 |

| #define INT_CAN0 54 |

| #define INT_CAN1 55 |

| #define INT_EMAC0 56 |

Referenced by EMACIntRegister(), and EMACIntUnregister().

| #define INT_HIBERNATE 57 |

| #define INT_USB0 58 |

| #define INT_PWM0_3 59 |

| #define INT_UDMA 60 |

| #define INT_UDMAERR 61 |

| #define INT_ADC1SS0 62 |

| #define INT_ADC1SS1 63 |

| #define INT_ADC1SS2 64 |

| #define INT_ADC1SS3 65 |

| #define INT_EPI0 66 |

| #define INT_GPIOJ 67 |

| #define INT_GPIOK 68 |

| #define INT_GPIOL 69 |

| #define INT_SSI2 70 |

| #define INT_SSI3 71 |

| #define INT_UART3 72 |

| #define INT_UART4 73 |

| #define INT_UART5 74 |

| #define INT_UART6 75 |

| #define INT_UART7 76 |

| #define INT_I2C2 77 |

| #define INT_I2C3 78 |

| #define INT_TIMER4A 79 |

| #define INT_TIMER4B 80 |

| #define INT_TIMER5A 81 |

| #define INT_TIMER5B 82 |

| #define INT_SYSEXC 83 |

| #define INT_I2C4 86 |

| #define INT_I2C5 87 |

| #define INT_GPIOM 88 |

| #define INT_GPION 89 |

| #define INT_TAMPER0 91 |

| #define INT_GPIOP0 92 |

| #define INT_GPIOP1 93 |

| #define INT_GPIOP2 94 |

| #define INT_GPIOP3 95 |

| #define INT_GPIOP4 96 |

| #define INT_GPIOP5 97 |

| #define INT_GPIOP6 98 |

| #define INT_GPIOP7 99 |

| #define INT_GPIOQ0 100 |

| #define INT_GPIOQ1 101 |

| #define INT_GPIOQ2 102 |

| #define INT_GPIOQ3 103 |

| #define INT_GPIOQ4 104 |

| #define INT_GPIOQ5 105 |

| #define INT_GPIOQ6 106 |

| #define INT_GPIOQ7 107 |

| #define INT_GPIOR 108 |

| #define INT_GPIOS 109 |

| #define INT_SHA0 110 |

Referenced by SHAMD5IntRegister(), and SHAMD5IntUnregister().

| #define INT_AES0 111 |

Referenced by AESIntRegister(), and AESIntUnregister().

| #define INT_DES0 112 |

Referenced by DESIntRegister(), and DESIntUnregister().

| #define INT_LCD0 113 |

Referenced by LCDIntRegister(), and LCDIntUnregister().

| #define INT_TIMER6A 114 |

| #define INT_TIMER6B 115 |

| #define INT_TIMER7A 116 |

| #define INT_TIMER7B 117 |

| #define INT_I2C6 118 |

| #define INT_I2C7 119 |

| #define INT_ONEWIRE0 121 |

| #define INT_I2C8 125 |

| #define INT_I2C9 126 |

| #define INT_GPIOT 127 |

| #define NUM_INTERRUPTS 129 |

| #define NUM_PRIORITY 8 |

Referenced by IntPriorityGroupingGet(), and IntPriorityGroupingSet().

| #define NUM_PRIORITY_BITS 3 |

| #define INT_PRIORITY_MASK ((0xFF << (8 - NUM_PRIORITY_BITS)) & 0xFF) |

| bool IntMasterEnable | ( | void | ) |