|

|

|

MSP432E4 DriverLib API Guide

1.11.00.03

|

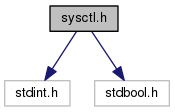

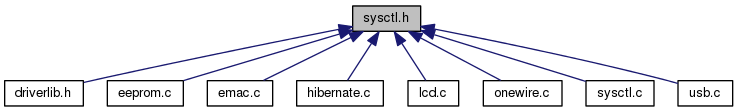

#include <stdint.h>#include <stdbool.h>

Go to the source code of this file.

Macros | |

| #define | SYSCTL_PERIPH_ADC0 0xf0003800 |

| #define | SYSCTL_PERIPH_ADC1 0xf0003801 |

| #define | SYSCTL_PERIPH_CAN0 0xf0003400 |

| #define | SYSCTL_PERIPH_CAN1 0xf0003401 |

| #define | SYSCTL_PERIPH_COMP0 0xf0003c00 |

| #define | SYSCTL_PERIPH_EMAC0 0xf0009c00 |

| #define | SYSCTL_PERIPH_EPHY0 0xf0003000 |

| #define | SYSCTL_PERIPH_EPI0 0xf0001000 |

| #define | SYSCTL_PERIPH_GPIOA 0xf0000800 |

| #define | SYSCTL_PERIPH_GPIOB 0xf0000801 |

| #define | SYSCTL_PERIPH_GPIOC 0xf0000802 |

| #define | SYSCTL_PERIPH_GPIOD 0xf0000803 |

| #define | SYSCTL_PERIPH_GPIOE 0xf0000804 |

| #define | SYSCTL_PERIPH_GPIOF 0xf0000805 |

| #define | SYSCTL_PERIPH_GPIOG 0xf0000806 |

| #define | SYSCTL_PERIPH_GPIOH 0xf0000807 |

| #define | SYSCTL_PERIPH_GPIOJ 0xf0000808 |

| #define | SYSCTL_PERIPH_HIBERNATE 0xf0001400 |

| #define | SYSCTL_PERIPH_CCM0 0xf0007400 |

| #define | SYSCTL_PERIPH_EEPROM0 0xf0005800 |

| #define | SYSCTL_PERIPH_GPIOK 0xf0000809 |

| #define | SYSCTL_PERIPH_GPIOL 0xf000080a |

| #define | SYSCTL_PERIPH_GPIOM 0xf000080b |

| #define | SYSCTL_PERIPH_GPION 0xf000080c |

| #define | SYSCTL_PERIPH_GPIOP 0xf000080d |

| #define | SYSCTL_PERIPH_GPIOQ 0xf000080e |

| #define | SYSCTL_PERIPH_GPIOR 0xf000080f |

| #define | SYSCTL_PERIPH_GPIOS 0xf0000810 |

| #define | SYSCTL_PERIPH_GPIOT 0xf0000811 |

| #define | SYSCTL_PERIPH_I2C0 0xf0002000 |

| #define | SYSCTL_PERIPH_I2C1 0xf0002001 |

| #define | SYSCTL_PERIPH_I2C2 0xf0002002 |

| #define | SYSCTL_PERIPH_I2C3 0xf0002003 |

| #define | SYSCTL_PERIPH_I2C4 0xf0002004 |

| #define | SYSCTL_PERIPH_I2C5 0xf0002005 |

| #define | SYSCTL_PERIPH_I2C6 0xf0002006 |

| #define | SYSCTL_PERIPH_I2C7 0xf0002007 |

| #define | SYSCTL_PERIPH_I2C8 0xf0002008 |

| #define | SYSCTL_PERIPH_I2C9 0xf0002009 |

| #define | SYSCTL_PERIPH_LCD0 0xf0009000 |

| #define | SYSCTL_PERIPH_ONEWIRE0 0xf0009800 |

| #define | SYSCTL_PERIPH_PWM0 0xf0004000 |

| #define | SYSCTL_PERIPH_PWM1 0xf0004001 |

| #define | SYSCTL_PERIPH_QEI0 0xf0004400 |

| #define | SYSCTL_PERIPH_QEI1 0xf0004401 |

| #define | SYSCTL_PERIPH_SSI0 0xf0001c00 |

| #define | SYSCTL_PERIPH_SSI1 0xf0001c01 |

| #define | SYSCTL_PERIPH_SSI2 0xf0001c02 |

| #define | SYSCTL_PERIPH_SSI3 0xf0001c03 |

| #define | SYSCTL_PERIPH_TIMER0 0xf0000400 |

| #define | SYSCTL_PERIPH_TIMER1 0xf0000401 |

| #define | SYSCTL_PERIPH_TIMER2 0xf0000402 |

| #define | SYSCTL_PERIPH_TIMER3 0xf0000403 |

| #define | SYSCTL_PERIPH_TIMER4 0xf0000404 |

| #define | SYSCTL_PERIPH_TIMER5 0xf0000405 |

| #define | SYSCTL_PERIPH_TIMER6 0xf0000406 |

| #define | SYSCTL_PERIPH_TIMER7 0xf0000407 |

| #define | SYSCTL_PERIPH_UART0 0xf0001800 |

| #define | SYSCTL_PERIPH_UART1 0xf0001801 |

| #define | SYSCTL_PERIPH_UART2 0xf0001802 |

| #define | SYSCTL_PERIPH_UART3 0xf0001803 |

| #define | SYSCTL_PERIPH_UART4 0xf0001804 |

| #define | SYSCTL_PERIPH_UART5 0xf0001805 |

| #define | SYSCTL_PERIPH_UART6 0xf0001806 |

| #define | SYSCTL_PERIPH_UART7 0xf0001807 |

| #define | SYSCTL_PERIPH_UDMA 0xf0000c00 |

| #define | SYSCTL_PERIPH_USB0 0xf0002800 |

| #define | SYSCTL_PERIPH_WDOG0 0xf0000000 |

| #define | SYSCTL_PERIPH_WDOG1 0xf0000001 |

| #define | SYSCTL_LDO_0_90V 0x80000012 |

| #define | SYSCTL_LDO_0_95V 0x80000013 |

| #define | SYSCTL_LDO_1_00V 0x80000014 |

| #define | SYSCTL_LDO_1_05V 0x80000015 |

| #define | SYSCTL_LDO_1_10V 0x80000016 |

| #define | SYSCTL_LDO_1_15V 0x80000017 |

| #define | SYSCTL_LDO_1_20V 0x80000018 |

| #define | SYSCTL_INT_BOR0 0x00000800 |

| #define | SYSCTL_INT_VDDA_OK 0x00000400 |

| #define | SYSCTL_INT_MOSC_PUP 0x00000100 |

| #define | SYSCTL_INT_USBPLL_LOCK 0x00000080 |

| #define | SYSCTL_INT_PLL_LOCK 0x00000040 |

| #define | SYSCTL_INT_MOSC_FAIL 0x00000008 |

| #define | SYSCTL_INT_BOR1 0x00000002 |

| #define | SYSCTL_INT_BOR 0x00000002 |

| #define | SYSCTL_CAUSE_HSRVREQ 0x00001000 |

| #define | SYSCTL_CAUSE_HIB 0x00000040 |

| #define | SYSCTL_CAUSE_WDOG1 0x00000020 |

| #define | SYSCTL_CAUSE_SW 0x00000010 |

| #define | SYSCTL_CAUSE_WDOG0 0x00000008 |

| #define | SYSCTL_CAUSE_BOR 0x00000004 |

| #define | SYSCTL_CAUSE_POR 0x00000002 |

| #define | SYSCTL_CAUSE_EXT 0x00000001 |

| #define | SYSCTL_BOR_RESET 0x00000002 |

| #define | SYSCTL_BOR_RESAMPLE 0x00000001 |

| #define | SYSCTL_CFG_VCO_240 0xF1000000 |

| #define | SYSCTL_CFG_VCO_160 0xF0000000 |

| #define | SYSCTL_USE_PLL 0x00000000 |

| #define | SYSCTL_USE_OSC 0x00003800 |

| #define | SYSCTL_XTAL_5MHZ 0x00000000 |

| #define | SYSCTL_XTAL_6MHZ 0x00000040 |

| #define | SYSCTL_XTAL_8MHZ 0x00000080 |

| #define | SYSCTL_XTAL_10MHZ 0x000000C0 |

| #define | SYSCTL_XTAL_12MHZ 0x00000100 |

| #define | SYSCTL_XTAL_16MHZ 0x00000140 |

| #define | SYSCTL_XTAL_18MHZ 0x00000180 |

| #define | SYSCTL_XTAL_20MHZ 0x000001C0 |

| #define | SYSCTL_XTAL_24MHZ 0x00000200 |

| #define | SYSCTL_XTAL_25MHZ 0x00000240 |

| #define | SYSCTL_OSC_MAIN 0x00000000 |

| #define | SYSCTL_OSC_INT 0x00000010 |

| #define | SYSCTL_OSC_INT30 0x00000030 |

| #define | SYSCTL_OSC_EXT32 0x80000038 |

| #define | SYSCTL_CFG_VCO_480 SYSCTL_CFG_VCO_240 |

| #define | SYSCTL_CFG_VCO_320 SYSCTL_CFG_VCO_160 |

| #define | SYSCTL_DSLP_OSC_MAIN 0x00000000 |

| #define | SYSCTL_DSLP_OSC_INT 0x00000010 |

| #define | SYSCTL_DSLP_OSC_INT30 0x00000030 |

| #define | SYSCTL_DSLP_OSC_EXT32 0x00000070 |

| #define | SYSCTL_DSLP_PIOSC_PD 0x00000002 |

| #define | SYSCTL_DSLP_MOSC_DPD 0x40000000 |

| #define | SYSCTL_PIOSC_CAL_AUTO 0x00000200 |

| #define | SYSCTL_PIOSC_CAL_FACT 0x00000100 |

| #define | SYSCTL_PIOSC_CAL_USER 0x80000100 |

| #define | SYSCTL_MOSC_VALIDATE 0x00000001 |

| #define | SYSCTL_MOSC_INTERRUPT 0x00000002 |

| #define | SYSCTL_MOSC_NO_XTAL 0x00000004 |

| #define | SYSCTL_MOSC_PWR_DIS 0x00000008 |

| #define | SYSCTL_MOSC_LOWFREQ 0x00000000 |

| #define | SYSCTL_MOSC_HIGHFREQ 0x00000010 |

| #define | SYSCTL_MOSC_SESRC 0x00000020 |

| #define | SYSCTL_LDO_SLEEP 0x00000200 |

| #define | SYSCTL_TEMP_LOW_POWER 0x00000100 |

| #define | SYSCTL_FLASH_NORMAL 0x00000000 |

| #define | SYSCTL_FLASH_LOW_POWER 0x00000020 |

| #define | SYSCTL_SRAM_NORMAL 0x00000000 |

| #define | SYSCTL_SRAM_STANDBY 0x00000001 |

| #define | SYSCTL_SRAM_LOW_POWER 0x00000003 |

| #define | SYSCTL_ONRST_WDOG0_POR 0x00000030 |

| #define | SYSCTL_ONRST_WDOG0_SYS 0x00000020 |

| #define | SYSCTL_ONRST_WDOG1_POR 0x000000C0 |

| #define | SYSCTL_ONRST_WDOG1_SYS 0x00000080 |

| #define | SYSCTL_ONRST_BOR_POR 0x0000000C |

| #define | SYSCTL_ONRST_BOR_SYS 0x00000008 |

| #define | SYSCTL_ONRST_EXT_POR 0x00000003 |

| #define | SYSCTL_ONRST_EXT_SYS 0x00000002 |

| #define | SYSCTL_VEVENT_VDDABO_NONE 0x00000000 |

| #define | SYSCTL_VEVENT_VDDABO_INT 0x00000100 |

| #define | SYSCTL_VEVENT_VDDABO_NMI 0x00000200 |

| #define | SYSCTL_VEVENT_VDDABO_RST 0x00000300 |

| #define | SYSCTL_VEVENT_VDDBO_NONE 0x00000000 |

| #define | SYSCTL_VEVENT_VDDBO_INT 0x00000001 |

| #define | SYSCTL_VEVENT_VDDBO_NMI 0x00000002 |

| #define | SYSCTL_VEVENT_VDDBO_RST 0x00000003 |

| #define | SYSCTL_VESTAT_VDDBOR 0x00000040 |

| #define | SYSCTL_VESTAT_VDDABOR 0x00000010 |

| #define | SYSCTL_NMI_MOSCFAIL 0x00010000 |

| #define | SYSCTL_NMI_TAMPER 0x00000200 |

| #define | SYSCTL_NMI_WDT1 0x00000020 |

| #define | SYSCTL_NMI_WDT0 0x00000008 |

| #define | SYSCTL_NMI_POWER 0x00000004 |

| #define | SYSCTL_NMI_EXTERNAL 0x00000001 |

| #define | SYSCTL_CLKOUT_EN 0x80000000 |

| #define | SYSCTL_CLKOUT_DIS 0x00000000 |

| #define | SYSCTL_CLKOUT_SYSCLK 0x00000000 |

| #define | SYSCTL_CLKOUT_PIOSC 0x00010000 |

| #define | SYSCTL_CLKOUT_MOSC 0x00020000 |

| #define | SYSCTL_ALTCLK_PIOSC 0x00000000 |

| #define | SYSCTL_ALTCLK_RTCOSC 0x00000003 |

| #define | SYSCTL_ALTCLK_LFIOSC 0x00000004 |

Functions | |

| uint32_t | SysCtlSRAMSizeGet (void) |

| uint32_t | SysCtlFlashSizeGet (void) |

| uint32_t | SysCtlFlashSectorSizeGet (void) |

| bool | SysCtlPeripheralPresent (uint32_t ui32Peripheral) |

| bool | SysCtlPeripheralReady (uint32_t ui32Peripheral) |

| void | SysCtlPeripheralPowerOn (uint32_t ui32Peripheral) |

| void | SysCtlPeripheralPowerOff (uint32_t ui32Peripheral) |

| void | SysCtlPeripheralReset (uint32_t ui32Peripheral) |

| void | SysCtlPeripheralEnable (uint32_t ui32Peripheral) |

| void | SysCtlPeripheralDisable (uint32_t ui32Peripheral) |

| void | SysCtlPeripheralSleepEnable (uint32_t ui32Peripheral) |

| void | SysCtlPeripheralSleepDisable (uint32_t ui32Peripheral) |

| void | SysCtlPeripheralDeepSleepEnable (uint32_t ui32Peripheral) |

| void | SysCtlPeripheralDeepSleepDisable (uint32_t ui32Peripheral) |

| void | SysCtlPeripheralClockGating (bool bEnable) |

| void | SysCtlIntRegister (void(*pfnHandler)(void)) |

| void | SysCtlIntUnregister (void) |

| void | SysCtlIntEnable (uint32_t ui32Ints) |

| void | SysCtlIntDisable (uint32_t ui32Ints) |

| void | SysCtlIntClear (uint32_t ui32Ints) |

| uint32_t | SysCtlIntStatus (bool bMasked) |

| void | SysCtlLDODeepSleepSet (uint32_t ui32Voltage) |

| uint32_t | SysCtlLDODeepSleepGet (void) |

| void | SysCtlSleepPowerSet (uint32_t ui32Config) |

| void | SysCtlDeepSleepPowerSet (uint32_t ui32Config) |

| void | SysCtlReset (void) |

| void | SysCtlSleep (void) |

| void | SysCtlDeepSleep (void) |

| uint32_t | SysCtlResetCauseGet (void) |

| void | SysCtlResetCauseClear (uint32_t ui32Causes) |

| void | SysCtlBrownOutConfigSet (uint32_t ui32Config, uint32_t ui32Delay) |

| void | SysCtlDelay (uint32_t ui32Count) |

| void | SysCtlMOSCConfigSet (uint32_t ui32Config) |

| uint32_t | SysCtlPIOSCCalibrate (uint32_t ui32Type) |

| void | SysCtlDeepSleepClockConfigSet (uint32_t ui32Div, uint32_t ui32Config) |

| uint32_t | SysCtlClockFreqSet (uint32_t ui32Config, uint32_t ui32SysClock) |

| void | SysCtlResetBehaviorSet (uint32_t ui32Behavior) |

| uint32_t | SysCtlResetBehaviorGet (void) |

| void | SysCtlClockOutConfig (uint32_t ui32Config, uint32_t ui32Div) |

| void | SysCtlAltClkConfig (uint32_t ui32Config) |

| uint32_t | SysCtlNMIStatus (void) |

| void | SysCtlNMIClear (uint32_t ui32Status) |

| void | SysCtlVoltageEventConfig (uint32_t ui32Config) |

| uint32_t | SysCtlVoltageEventStatus (void) |

| void | SysCtlVoltageEventClear (uint32_t ui32Status) |

| bool | SysCtlVCOGet (uint32_t ui32Crystal, uint32_t *pui32VCOFrequency) |

| #define SYSCTL_PERIPH_ADC0 0xf0003800 |

| #define SYSCTL_PERIPH_ADC1 0xf0003801 |

| #define SYSCTL_PERIPH_CAN0 0xf0003400 |

| #define SYSCTL_PERIPH_CAN1 0xf0003401 |

| #define SYSCTL_PERIPH_COMP0 0xf0003c00 |

| #define SYSCTL_PERIPH_EMAC0 0xf0009c00 |

| #define SYSCTL_PERIPH_EPHY0 0xf0003000 |

Referenced by EMACPHYConfigSet().

| #define SYSCTL_PERIPH_EPI0 0xf0001000 |

| #define SYSCTL_PERIPH_GPIOA 0xf0000800 |

| #define SYSCTL_PERIPH_GPIOB 0xf0000801 |

| #define SYSCTL_PERIPH_GPIOC 0xf0000802 |

| #define SYSCTL_PERIPH_GPIOD 0xf0000803 |

| #define SYSCTL_PERIPH_GPIOE 0xf0000804 |

| #define SYSCTL_PERIPH_GPIOF 0xf0000805 |

| #define SYSCTL_PERIPH_GPIOG 0xf0000806 |

| #define SYSCTL_PERIPH_GPIOH 0xf0000807 |

| #define SYSCTL_PERIPH_GPIOJ 0xf0000808 |

| #define SYSCTL_PERIPH_HIBERNATE 0xf0001400 |

| #define SYSCTL_PERIPH_CCM0 0xf0007400 |

| #define SYSCTL_PERIPH_EEPROM0 0xf0005800 |

| #define SYSCTL_PERIPH_GPIOK 0xf0000809 |

| #define SYSCTL_PERIPH_GPIOL 0xf000080a |

| #define SYSCTL_PERIPH_GPIOM 0xf000080b |

| #define SYSCTL_PERIPH_GPION 0xf000080c |

| #define SYSCTL_PERIPH_GPIOP 0xf000080d |

| #define SYSCTL_PERIPH_GPIOQ 0xf000080e |

| #define SYSCTL_PERIPH_GPIOR 0xf000080f |

| #define SYSCTL_PERIPH_GPIOS 0xf0000810 |

| #define SYSCTL_PERIPH_GPIOT 0xf0000811 |

| #define SYSCTL_PERIPH_I2C0 0xf0002000 |

| #define SYSCTL_PERIPH_I2C1 0xf0002001 |

| #define SYSCTL_PERIPH_I2C2 0xf0002002 |

| #define SYSCTL_PERIPH_I2C3 0xf0002003 |

| #define SYSCTL_PERIPH_I2C4 0xf0002004 |

| #define SYSCTL_PERIPH_I2C5 0xf0002005 |

| #define SYSCTL_PERIPH_I2C6 0xf0002006 |

| #define SYSCTL_PERIPH_I2C7 0xf0002007 |

| #define SYSCTL_PERIPH_I2C8 0xf0002008 |

| #define SYSCTL_PERIPH_I2C9 0xf0002009 |

| #define SYSCTL_PERIPH_LCD0 0xf0009000 |

| #define SYSCTL_PERIPH_ONEWIRE0 0xf0009800 |

| #define SYSCTL_PERIPH_PWM0 0xf0004000 |

| #define SYSCTL_PERIPH_PWM1 0xf0004001 |

| #define SYSCTL_PERIPH_QEI0 0xf0004400 |

| #define SYSCTL_PERIPH_QEI1 0xf0004401 |

| #define SYSCTL_PERIPH_SSI0 0xf0001c00 |

| #define SYSCTL_PERIPH_SSI1 0xf0001c01 |

| #define SYSCTL_PERIPH_SSI2 0xf0001c02 |

| #define SYSCTL_PERIPH_SSI3 0xf0001c03 |

| #define SYSCTL_PERIPH_TIMER0 0xf0000400 |

| #define SYSCTL_PERIPH_TIMER1 0xf0000401 |

| #define SYSCTL_PERIPH_TIMER2 0xf0000402 |

| #define SYSCTL_PERIPH_TIMER3 0xf0000403 |

| #define SYSCTL_PERIPH_TIMER4 0xf0000404 |

| #define SYSCTL_PERIPH_TIMER5 0xf0000405 |

| #define SYSCTL_PERIPH_TIMER6 0xf0000406 |

| #define SYSCTL_PERIPH_TIMER7 0xf0000407 |

| #define SYSCTL_PERIPH_UART0 0xf0001800 |

| #define SYSCTL_PERIPH_UART1 0xf0001801 |

| #define SYSCTL_PERIPH_UART2 0xf0001802 |

| #define SYSCTL_PERIPH_UART3 0xf0001803 |

| #define SYSCTL_PERIPH_UART4 0xf0001804 |

| #define SYSCTL_PERIPH_UART5 0xf0001805 |

| #define SYSCTL_PERIPH_UART6 0xf0001806 |

| #define SYSCTL_PERIPH_UART7 0xf0001807 |

| #define SYSCTL_PERIPH_UDMA 0xf0000c00 |

| #define SYSCTL_PERIPH_USB0 0xf0002800 |

| #define SYSCTL_PERIPH_WDOG0 0xf0000000 |

| #define SYSCTL_PERIPH_WDOG1 0xf0000001 |

| #define SYSCTL_LDO_0_90V 0x80000012 |

Referenced by SysCtlLDODeepSleepSet().

| #define SYSCTL_LDO_0_95V 0x80000013 |

Referenced by SysCtlLDODeepSleepSet().

| #define SYSCTL_LDO_1_00V 0x80000014 |

Referenced by SysCtlLDODeepSleepSet().

| #define SYSCTL_LDO_1_05V 0x80000015 |

Referenced by SysCtlLDODeepSleepSet().

| #define SYSCTL_LDO_1_10V 0x80000016 |

Referenced by SysCtlLDODeepSleepSet().

| #define SYSCTL_LDO_1_15V 0x80000017 |

Referenced by SysCtlLDODeepSleepSet().

| #define SYSCTL_LDO_1_20V 0x80000018 |

Referenced by SysCtlLDODeepSleepSet().

| #define SYSCTL_INT_BOR0 0x00000800 |

| #define SYSCTL_INT_VDDA_OK 0x00000400 |

| #define SYSCTL_INT_MOSC_PUP 0x00000100 |

| #define SYSCTL_INT_USBPLL_LOCK 0x00000080 |

| #define SYSCTL_INT_PLL_LOCK 0x00000040 |

| #define SYSCTL_INT_MOSC_FAIL 0x00000008 |

| #define SYSCTL_INT_BOR1 0x00000002 |

| #define SYSCTL_INT_BOR 0x00000002 |

| #define SYSCTL_CAUSE_HSRVREQ 0x00001000 |

| #define SYSCTL_CAUSE_HIB 0x00000040 |

| #define SYSCTL_CAUSE_WDOG1 0x00000020 |

| #define SYSCTL_CAUSE_SW 0x00000010 |

| #define SYSCTL_CAUSE_WDOG0 0x00000008 |

| #define SYSCTL_CAUSE_BOR 0x00000004 |

| #define SYSCTL_CAUSE_POR 0x00000002 |

| #define SYSCTL_CAUSE_EXT 0x00000001 |

| #define SYSCTL_BOR_RESET 0x00000002 |

| #define SYSCTL_BOR_RESAMPLE 0x00000001 |

| #define SYSCTL_CFG_VCO_240 0xF1000000 |

| #define SYSCTL_CFG_VCO_160 0xF0000000 |

| #define SYSCTL_USE_PLL 0x00000000 |

| #define SYSCTL_USE_OSC 0x00003800 |

| #define SYSCTL_XTAL_5MHZ 0x00000000 |

Referenced by SysCtlClockFreqSet().

| #define SYSCTL_XTAL_6MHZ 0x00000040 |

| #define SYSCTL_XTAL_8MHZ 0x00000080 |

| #define SYSCTL_XTAL_10MHZ 0x000000C0 |

| #define SYSCTL_XTAL_12MHZ 0x00000100 |

| #define SYSCTL_XTAL_16MHZ 0x00000140 |

Referenced by SysCtlClockFreqSet().

| #define SYSCTL_XTAL_18MHZ 0x00000180 |

| #define SYSCTL_XTAL_20MHZ 0x000001C0 |

| #define SYSCTL_XTAL_24MHZ 0x00000200 |

| #define SYSCTL_XTAL_25MHZ 0x00000240 |

Referenced by SysCtlClockFreqSet().

| #define SYSCTL_OSC_MAIN 0x00000000 |

Referenced by SysCtlClockFreqSet().

| #define SYSCTL_OSC_INT 0x00000010 |

Referenced by SysCtlClockFreqSet().

| #define SYSCTL_OSC_INT30 0x00000030 |

Referenced by SysCtlClockFreqSet().

| #define SYSCTL_OSC_EXT32 0x80000038 |

Referenced by SysCtlClockFreqSet().

| #define SYSCTL_CFG_VCO_480 SYSCTL_CFG_VCO_240 |

| #define SYSCTL_CFG_VCO_320 SYSCTL_CFG_VCO_160 |

| #define SYSCTL_DSLP_OSC_MAIN 0x00000000 |

Referenced by SysCtlDeepSleepClockConfigSet().

| #define SYSCTL_DSLP_OSC_INT 0x00000010 |

Referenced by SysCtlDeepSleepClockConfigSet().

| #define SYSCTL_DSLP_OSC_INT30 0x00000030 |

Referenced by SysCtlDeepSleepClockConfigSet().

| #define SYSCTL_DSLP_OSC_EXT32 0x00000070 |

Referenced by SysCtlDeepSleepClockConfigSet().

| #define SYSCTL_DSLP_PIOSC_PD 0x00000002 |

Referenced by SysCtlDeepSleepClockConfigSet().

| #define SYSCTL_DSLP_MOSC_DPD 0x40000000 |

Referenced by SysCtlDeepSleepClockConfigSet().

| #define SYSCTL_PIOSC_CAL_AUTO 0x00000200 |

| #define SYSCTL_PIOSC_CAL_FACT 0x00000100 |

| #define SYSCTL_PIOSC_CAL_USER 0x80000100 |

| #define SYSCTL_MOSC_VALIDATE 0x00000001 |

| #define SYSCTL_MOSC_INTERRUPT 0x00000002 |

| #define SYSCTL_MOSC_NO_XTAL 0x00000004 |

| #define SYSCTL_MOSC_PWR_DIS 0x00000008 |

| #define SYSCTL_MOSC_LOWFREQ 0x00000000 |

| #define SYSCTL_MOSC_HIGHFREQ 0x00000010 |

| #define SYSCTL_MOSC_SESRC 0x00000020 |

| #define SYSCTL_LDO_SLEEP 0x00000200 |

| #define SYSCTL_TEMP_LOW_POWER 0x00000100 |

| #define SYSCTL_FLASH_NORMAL 0x00000000 |

| #define SYSCTL_FLASH_LOW_POWER 0x00000020 |

| #define SYSCTL_SRAM_NORMAL 0x00000000 |

| #define SYSCTL_SRAM_STANDBY 0x00000001 |

| #define SYSCTL_SRAM_LOW_POWER 0x00000003 |

| #define SYSCTL_ONRST_WDOG0_POR 0x00000030 |

| #define SYSCTL_ONRST_WDOG0_SYS 0x00000020 |

| #define SYSCTL_ONRST_WDOG1_POR 0x000000C0 |

| #define SYSCTL_ONRST_WDOG1_SYS 0x00000080 |

| #define SYSCTL_ONRST_BOR_POR 0x0000000C |

| #define SYSCTL_ONRST_BOR_SYS 0x00000008 |

| #define SYSCTL_ONRST_EXT_POR 0x00000003 |

| #define SYSCTL_ONRST_EXT_SYS 0x00000002 |

| #define SYSCTL_VEVENT_VDDABO_NONE 0x00000000 |

| #define SYSCTL_VEVENT_VDDABO_INT 0x00000100 |

| #define SYSCTL_VEVENT_VDDABO_NMI 0x00000200 |

| #define SYSCTL_VEVENT_VDDABO_RST 0x00000300 |

| #define SYSCTL_VEVENT_VDDBO_NONE 0x00000000 |

| #define SYSCTL_VEVENT_VDDBO_INT 0x00000001 |

| #define SYSCTL_VEVENT_VDDBO_NMI 0x00000002 |

| #define SYSCTL_VEVENT_VDDBO_RST 0x00000003 |

| #define SYSCTL_VESTAT_VDDBOR 0x00000040 |

| #define SYSCTL_VESTAT_VDDABOR 0x00000010 |

| #define SYSCTL_NMI_MOSCFAIL 0x00010000 |

| #define SYSCTL_NMI_TAMPER 0x00000200 |

| #define SYSCTL_NMI_WDT1 0x00000020 |

| #define SYSCTL_NMI_WDT0 0x00000008 |

| #define SYSCTL_NMI_POWER 0x00000004 |

| #define SYSCTL_NMI_EXTERNAL 0x00000001 |

| #define SYSCTL_CLKOUT_EN 0x80000000 |

Referenced by SysCtlClockOutConfig().

| #define SYSCTL_CLKOUT_DIS 0x00000000 |

Referenced by SysCtlClockOutConfig().

| #define SYSCTL_CLKOUT_SYSCLK 0x00000000 |

Referenced by SysCtlClockOutConfig().

| #define SYSCTL_CLKOUT_PIOSC 0x00010000 |

Referenced by SysCtlClockOutConfig().

| #define SYSCTL_CLKOUT_MOSC 0x00020000 |

Referenced by SysCtlClockOutConfig().

| #define SYSCTL_ALTCLK_PIOSC 0x00000000 |

| #define SYSCTL_ALTCLK_RTCOSC 0x00000003 |

| #define SYSCTL_ALTCLK_LFIOSC 0x00000004 |

| void SysCtlBrownOutConfigSet | ( | uint32_t | ui32Config, |

| uint32_t | ui32Delay | ||

| ) |

| void SysCtlDelay | ( | uint32_t | ui32Count | ) |

Referenced by EEPROMInit(), EEPROMProgram(), EMACPHYConfigSet(), LCDClockReset(), OneWireDMAEnable(), and SysCtlResetCauseClear().