|

|

|

MSP432E4 DriverLib API Guide

1.11.00.03

|

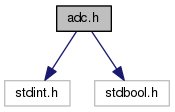

#include <stdint.h>#include <stdbool.h>

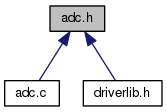

Go to the source code of this file.

Macros | |

| #define | ADC_TRIGGER_PROCESSOR 0x00000000 |

| #define | ADC_TRIGGER_COMP0 0x00000001 |

| #define | ADC_TRIGGER_COMP1 0x00000002 |

| #define | ADC_TRIGGER_COMP2 0x00000003 |

| #define | ADC_TRIGGER_EXTERNAL 0x00000004 |

| #define | ADC_TRIGGER_TIMER 0x00000005 |

| #define | ADC_TRIGGER_PWM0 0x00000006 |

| #define | ADC_TRIGGER_PWM1 0x00000007 |

| #define | ADC_TRIGGER_PWM2 0x00000008 |

| #define | ADC_TRIGGER_PWM3 0x00000009 |

| #define | ADC_TRIGGER_NEVER 0x0000000E |

| #define | ADC_TRIGGER_ALWAYS 0x0000000F |

| #define | ADC_CTL_TS 0x00000080 |

| #define | ADC_CTL_IE 0x00000040 |

| #define | ADC_CTL_END 0x00000020 |

| #define | ADC_CTL_D 0x00000010 |

| #define | ADC_CTL_CH0 0x00000000 |

| #define | ADC_CTL_CH1 0x00000001 |

| #define | ADC_CTL_CH2 0x00000002 |

| #define | ADC_CTL_CH3 0x00000003 |

| #define | ADC_CTL_CH4 0x00000004 |

| #define | ADC_CTL_CH5 0x00000005 |

| #define | ADC_CTL_CH6 0x00000006 |

| #define | ADC_CTL_CH7 0x00000007 |

| #define | ADC_CTL_CH8 0x00000008 |

| #define | ADC_CTL_CH9 0x00000009 |

| #define | ADC_CTL_CH10 0x0000000A |

| #define | ADC_CTL_CH11 0x0000000B |

| #define | ADC_CTL_CH12 0x0000000C |

| #define | ADC_CTL_CH13 0x0000000D |

| #define | ADC_CTL_CH14 0x0000000E |

| #define | ADC_CTL_CH15 0x0000000F |

| #define | ADC_CTL_CH16 0x00000100 |

| #define | ADC_CTL_CH17 0x00000101 |

| #define | ADC_CTL_CH18 0x00000102 |

| #define | ADC_CTL_CH19 0x00000103 |

| #define | ADC_CTL_CH20 0x00000104 |

| #define | ADC_CTL_CH21 0x00000105 |

| #define | ADC_CTL_CH22 0x00000106 |

| #define | ADC_CTL_CH23 0x00000107 |

| #define | ADC_CTL_CMP0 0x00080000 |

| #define | ADC_CTL_CMP1 0x00090000 |

| #define | ADC_CTL_CMP2 0x000A0000 |

| #define | ADC_CTL_CMP3 0x000B0000 |

| #define | ADC_CTL_CMP4 0x000C0000 |

| #define | ADC_CTL_CMP5 0x000D0000 |

| #define | ADC_CTL_CMP6 0x000E0000 |

| #define | ADC_CTL_CMP7 0x000F0000 |

| #define | ADC_CTL_SHOLD_4 0x00000000 |

| #define | ADC_CTL_SHOLD_8 0x00200000 |

| #define | ADC_CTL_SHOLD_16 0x00400000 |

| #define | ADC_CTL_SHOLD_32 0x00600000 |

| #define | ADC_CTL_SHOLD_64 0x00800000 |

| #define | ADC_CTL_SHOLD_128 0x00A00000 |

| #define | ADC_CTL_SHOLD_256 0x00C00000 |

| #define | ADC_COMP_TRIG_NONE 0x00000000 |

| #define | ADC_COMP_TRIG_LOW_ALWAYS 0x00001000 |

| #define | ADC_COMP_TRIG_LOW_ONCE 0x00001100 |

| #define | ADC_COMP_TRIG_LOW_HALWAYS 0x00001200 |

| #define | ADC_COMP_TRIG_LOW_HONCE 0x00001300 |

| #define | ADC_COMP_TRIG_MID_ALWAYS 0x00001400 |

| #define | ADC_COMP_TRIG_MID_ONCE 0x00001500 |

| #define | ADC_COMP_TRIG_HIGH_ALWAYS 0x00001C00 |

| #define | ADC_COMP_TRIG_HIGH_ONCE 0x00001D00 |

| #define | ADC_COMP_TRIG_HIGH_HALWAYS 0x00001E00 |

| #define | ADC_COMP_TRIG_HIGH_HONCE 0x00001F00 |

| #define | ADC_COMP_INT_NONE 0x00000000 |

| #define | ADC_COMP_INT_LOW_ALWAYS 0x00000010 |

| #define | ADC_COMP_INT_LOW_ONCE 0x00000011 |

| #define | ADC_COMP_INT_LOW_HALWAYS 0x00000012 |

| #define | ADC_COMP_INT_LOW_HONCE 0x00000013 |

| #define | ADC_COMP_INT_MID_ALWAYS 0x00000014 |

| #define | ADC_COMP_INT_MID_ONCE 0x00000015 |

| #define | ADC_COMP_INT_HIGH_ALWAYS 0x0000001C |

| #define | ADC_COMP_INT_HIGH_ONCE 0x0000001D |

| #define | ADC_COMP_INT_HIGH_HALWAYS 0x0000001E |

| #define | ADC_COMP_INT_HIGH_HONCE 0x0000001F |

| #define | ADC_TRIGGER_WAIT 0x08000000 |

| #define | ADC_TRIGGER_SIGNAL 0x80000000 |

| #define | ADC_PHASE_0 0x00000000 |

| #define | ADC_PHASE_22_5 0x00000001 |

| #define | ADC_PHASE_45 0x00000002 |

| #define | ADC_PHASE_67_5 0x00000003 |

| #define | ADC_PHASE_90 0x00000004 |

| #define | ADC_PHASE_112_5 0x00000005 |

| #define | ADC_PHASE_135 0x00000006 |

| #define | ADC_PHASE_157_5 0x00000007 |

| #define | ADC_PHASE_180 0x00000008 |

| #define | ADC_PHASE_202_5 0x00000009 |

| #define | ADC_PHASE_225 0x0000000A |

| #define | ADC_PHASE_247_5 0x0000000B |

| #define | ADC_PHASE_270 0x0000000C |

| #define | ADC_PHASE_292_5 0x0000000D |

| #define | ADC_PHASE_315 0x0000000E |

| #define | ADC_PHASE_337_5 0x0000000F |

| #define | ADC_REF_INT 0x00000000 |

| #define | ADC_REF_EXT_3V 0x00000001 |

| #define | ADC_INT_SS0 0x00000001 |

| #define | ADC_INT_SS1 0x00000002 |

| #define | ADC_INT_SS2 0x00000004 |

| #define | ADC_INT_SS3 0x00000008 |

| #define | ADC_INT_DMA_SS0 0x00000100 |

| #define | ADC_INT_DMA_SS1 0x00000200 |

| #define | ADC_INT_DMA_SS2 0x00000400 |

| #define | ADC_INT_DMA_SS3 0x00000800 |

| #define | ADC_INT_DCON_SS0 0x00010000 |

| #define | ADC_INT_DCON_SS1 0x00020000 |

| #define | ADC_INT_DCON_SS2 0x00040000 |

| #define | ADC_INT_DCON_SS3 0x00080000 |

| #define | ADC_CLOCK_RATE_FULL 0x00000070 |

| #define | ADC_CLOCK_RATE_HALF 0x00000050 |

| #define | ADC_CLOCK_RATE_FOURTH 0x00000030 |

| #define | ADC_CLOCK_RATE_EIGHTH 0x00000010 |

| #define | ADC_CLOCK_SRC_PLL 0x00000000 |

| #define | ADC_CLOCK_SRC_ALTCLK 0x00000001 |

| #define | ADC_CLOCK_SRC_MOSC 0x00000002 |

Functions | |

| void | ADCIntRegister (uint32_t ui32Base, uint32_t ui32SequenceNum, void(*pfnHandler)(void)) |

| void | ADCIntUnregister (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| void | ADCIntDisable (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| void | ADCIntEnable (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| uint32_t | ADCIntStatus (uint32_t ui32Base, uint32_t ui32SequenceNum, bool bMasked) |

| void | ADCIntClear (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| void | ADCSequenceEnable (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| void | ADCSequenceDisable (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| void | ADCSequenceConfigure (uint32_t ui32Base, uint32_t ui32SequenceNum, uint32_t ui32Trigger, uint32_t ui32Priority) |

| void | ADCSequenceStepConfigure (uint32_t ui32Base, uint32_t ui32SequenceNum, uint32_t ui32Step, uint32_t ui32Config) |

| int32_t | ADCSequenceOverflow (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| void | ADCSequenceOverflowClear (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| int32_t | ADCSequenceUnderflow (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| void | ADCSequenceUnderflowClear (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| int32_t | ADCSequenceDataGet (uint32_t ui32Base, uint32_t ui32SequenceNum, uint32_t *pui32Buffer) |

| void | ADCProcessorTrigger (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| void | ADCSoftwareOversampleConfigure (uint32_t ui32Base, uint32_t ui32SequenceNum, uint32_t ui32Factor) |

| void | ADCSoftwareOversampleStepConfigure (uint32_t ui32Base, uint32_t ui32SequenceNum, uint32_t ui32Step, uint32_t ui32Config) |

| void | ADCSoftwareOversampleDataGet (uint32_t ui32Base, uint32_t ui32SequenceNum, uint32_t *pui32Buffer, uint32_t ui32Count) |

| void | ADCHardwareOversampleConfigure (uint32_t ui32Base, uint32_t ui32Factor) |

| void | ADCClockConfigSet (uint32_t ui32Base, uint32_t ui32Config, uint32_t ui32ClockDiv) |

| uint32_t | ADCClockConfigGet (uint32_t ui32Base, uint32_t *pui32ClockDiv) |

| void | ADCComparatorConfigure (uint32_t ui32Base, uint32_t ui32Comp, uint32_t ui32Config) |

| void | ADCComparatorRegionSet (uint32_t ui32Base, uint32_t ui32Comp, uint32_t ui32LowRef, uint32_t ui32HighRef) |

| void | ADCComparatorReset (uint32_t ui32Base, uint32_t ui32Comp, bool bTrigger, bool bInterrupt) |

| void | ADCComparatorIntDisable (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| void | ADCComparatorIntEnable (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| uint32_t | ADCComparatorIntStatus (uint32_t ui32Base) |

| void | ADCComparatorIntClear (uint32_t ui32Base, uint32_t ui32Status) |

| void | ADCIntDisableEx (uint32_t ui32Base, uint32_t ui32IntFlags) |

| void | ADCIntEnableEx (uint32_t ui32Base, uint32_t ui32IntFlags) |

| uint32_t | ADCIntStatusEx (uint32_t ui32Base, bool bMasked) |

| void | ADCIntClearEx (uint32_t ui32Base, uint32_t ui32IntFlags) |

| void | ADCSequenceDMAEnable (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| void | ADCSequenceDMADisable (uint32_t ui32Base, uint32_t ui32SequenceNum) |

| bool | ADCBusy (uint32_t ui32Base) |

| void | ADCReferenceSet (uint32_t ui32Base, uint32_t ui32Ref) |

| uint32_t | ADCReferenceGet (uint32_t ui32Base) |

| void | ADCPhaseDelaySet (uint32_t ui32Base, uint32_t ui32Phase) |

| uint32_t | ADCPhaseDelayGet (uint32_t ui32Base) |

| void | ADCSampleRateSet (uint32_t ui32Base, uint32_t ui32ADCClock, uint32_t ui32Rate) |

| uint32_t | ADCSampleRateGet (uint32_t ui32Base) |

| #define ADC_TRIGGER_PROCESSOR 0x00000000 |

Referenced by ADCSequenceConfigure().

| #define ADC_TRIGGER_COMP0 0x00000001 |

Referenced by ADCSequenceConfigure().

| #define ADC_TRIGGER_COMP1 0x00000002 |

Referenced by ADCSequenceConfigure().

| #define ADC_TRIGGER_COMP2 0x00000003 |

Referenced by ADCSequenceConfigure().

| #define ADC_TRIGGER_EXTERNAL 0x00000004 |

Referenced by ADCSequenceConfigure().

| #define ADC_TRIGGER_TIMER 0x00000005 |

Referenced by ADCSequenceConfigure().

| #define ADC_TRIGGER_PWM0 0x00000006 |

Referenced by ADCSequenceConfigure().

| #define ADC_TRIGGER_PWM1 0x00000007 |

Referenced by ADCSequenceConfigure().

| #define ADC_TRIGGER_PWM2 0x00000008 |

Referenced by ADCSequenceConfigure().

| #define ADC_TRIGGER_PWM3 0x00000009 |

Referenced by ADCSequenceConfigure().

| #define ADC_TRIGGER_NEVER 0x0000000E |

| #define ADC_TRIGGER_ALWAYS 0x0000000F |

Referenced by ADCSequenceConfigure().

| #define ADC_CTL_TS 0x00000080 |

| #define ADC_CTL_IE 0x00000040 |

| #define ADC_CTL_END 0x00000020 |

| #define ADC_CTL_D 0x00000010 |

| #define ADC_CTL_CH0 0x00000000 |

| #define ADC_CTL_CH1 0x00000001 |

| #define ADC_CTL_CH2 0x00000002 |

| #define ADC_CTL_CH3 0x00000003 |

| #define ADC_CTL_CH4 0x00000004 |

| #define ADC_CTL_CH5 0x00000005 |

| #define ADC_CTL_CH6 0x00000006 |

| #define ADC_CTL_CH7 0x00000007 |

| #define ADC_CTL_CH8 0x00000008 |

| #define ADC_CTL_CH9 0x00000009 |

| #define ADC_CTL_CH10 0x0000000A |

| #define ADC_CTL_CH11 0x0000000B |

| #define ADC_CTL_CH12 0x0000000C |

| #define ADC_CTL_CH13 0x0000000D |

| #define ADC_CTL_CH14 0x0000000E |

| #define ADC_CTL_CH15 0x0000000F |

| #define ADC_CTL_CH16 0x00000100 |

| #define ADC_CTL_CH17 0x00000101 |

| #define ADC_CTL_CH18 0x00000102 |

| #define ADC_CTL_CH19 0x00000103 |

| #define ADC_CTL_CH20 0x00000104 |

| #define ADC_CTL_CH21 0x00000105 |

| #define ADC_CTL_CH22 0x00000106 |

| #define ADC_CTL_CH23 0x00000107 |

| #define ADC_CTL_CMP0 0x00080000 |

| #define ADC_CTL_CMP1 0x00090000 |

| #define ADC_CTL_CMP2 0x000A0000 |

| #define ADC_CTL_CMP3 0x000B0000 |

| #define ADC_CTL_CMP4 0x000C0000 |

| #define ADC_CTL_CMP5 0x000D0000 |

| #define ADC_CTL_CMP6 0x000E0000 |

| #define ADC_CTL_CMP7 0x000F0000 |

| #define ADC_CTL_SHOLD_4 0x00000000 |

| #define ADC_CTL_SHOLD_8 0x00200000 |

| #define ADC_CTL_SHOLD_16 0x00400000 |

| #define ADC_CTL_SHOLD_32 0x00600000 |

| #define ADC_CTL_SHOLD_64 0x00800000 |

| #define ADC_CTL_SHOLD_128 0x00A00000 |

| #define ADC_CTL_SHOLD_256 0x00C00000 |

| #define ADC_COMP_TRIG_NONE 0x00000000 |

| #define ADC_COMP_TRIG_LOW_ALWAYS 0x00001000 |

| #define ADC_COMP_TRIG_LOW_ONCE 0x00001100 |

| #define ADC_COMP_TRIG_LOW_HALWAYS 0x00001200 |

| #define ADC_COMP_TRIG_LOW_HONCE 0x00001300 |

| #define ADC_COMP_TRIG_MID_ALWAYS 0x00001400 |

| #define ADC_COMP_TRIG_MID_ONCE 0x00001500 |

| #define ADC_COMP_TRIG_HIGH_ALWAYS 0x00001C00 |

| #define ADC_COMP_TRIG_HIGH_ONCE 0x00001D00 |

| #define ADC_COMP_TRIG_HIGH_HALWAYS 0x00001E00 |

| #define ADC_COMP_TRIG_HIGH_HONCE 0x00001F00 |

| #define ADC_COMP_INT_NONE 0x00000000 |

| #define ADC_COMP_INT_LOW_ALWAYS 0x00000010 |

| #define ADC_COMP_INT_LOW_ONCE 0x00000011 |

| #define ADC_COMP_INT_LOW_HALWAYS 0x00000012 |

| #define ADC_COMP_INT_LOW_HONCE 0x00000013 |

| #define ADC_COMP_INT_MID_ALWAYS 0x00000014 |

| #define ADC_COMP_INT_MID_ONCE 0x00000015 |

| #define ADC_COMP_INT_HIGH_ALWAYS 0x0000001C |

| #define ADC_COMP_INT_HIGH_ONCE 0x0000001D |

| #define ADC_COMP_INT_HIGH_HALWAYS 0x0000001E |

| #define ADC_COMP_INT_HIGH_HONCE 0x0000001F |

| #define ADC_TRIGGER_WAIT 0x08000000 |

| #define ADC_TRIGGER_SIGNAL 0x80000000 |

| #define ADC_PHASE_0 0x00000000 |

Referenced by ADCPhaseDelaySet().

| #define ADC_PHASE_22_5 0x00000001 |

Referenced by ADCPhaseDelaySet().

| #define ADC_PHASE_45 0x00000002 |

Referenced by ADCPhaseDelaySet().

| #define ADC_PHASE_67_5 0x00000003 |

Referenced by ADCPhaseDelaySet().

| #define ADC_PHASE_90 0x00000004 |

Referenced by ADCPhaseDelaySet().

| #define ADC_PHASE_112_5 0x00000005 |

Referenced by ADCPhaseDelaySet().

| #define ADC_PHASE_135 0x00000006 |

Referenced by ADCPhaseDelaySet().

| #define ADC_PHASE_157_5 0x00000007 |

Referenced by ADCPhaseDelaySet().

| #define ADC_PHASE_180 0x00000008 |

Referenced by ADCPhaseDelaySet().

| #define ADC_PHASE_202_5 0x00000009 |

Referenced by ADCPhaseDelaySet().

| #define ADC_PHASE_225 0x0000000A |

Referenced by ADCPhaseDelaySet().

| #define ADC_PHASE_247_5 0x0000000B |

Referenced by ADCPhaseDelaySet().

| #define ADC_PHASE_270 0x0000000C |

Referenced by ADCPhaseDelaySet().

| #define ADC_PHASE_292_5 0x0000000D |

Referenced by ADCPhaseDelaySet().

| #define ADC_PHASE_315 0x0000000E |

Referenced by ADCPhaseDelaySet().

| #define ADC_PHASE_337_5 0x0000000F |

Referenced by ADCPhaseDelaySet().

| #define ADC_REF_INT 0x00000000 |

Referenced by ADCReferenceSet().

| #define ADC_REF_EXT_3V 0x00000001 |

Referenced by ADCReferenceSet().

| #define ADC_INT_SS0 0x00000001 |

| #define ADC_INT_SS1 0x00000002 |

| #define ADC_INT_SS2 0x00000004 |

| #define ADC_INT_SS3 0x00000008 |

| #define ADC_INT_DMA_SS0 0x00000100 |

| #define ADC_INT_DMA_SS1 0x00000200 |

| #define ADC_INT_DMA_SS2 0x00000400 |

| #define ADC_INT_DMA_SS3 0x00000800 |

| #define ADC_INT_DCON_SS0 0x00010000 |

Referenced by ADCIntStatusEx().

| #define ADC_INT_DCON_SS1 0x00020000 |

Referenced by ADCIntStatusEx().

| #define ADC_INT_DCON_SS2 0x00040000 |

Referenced by ADCIntStatusEx().

| #define ADC_INT_DCON_SS3 0x00080000 |

Referenced by ADCIntStatusEx().

| #define ADC_CLOCK_RATE_FULL 0x00000070 |

Referenced by ADCClockConfigSet().

| #define ADC_CLOCK_RATE_HALF 0x00000050 |

| #define ADC_CLOCK_RATE_FOURTH 0x00000030 |

| #define ADC_CLOCK_RATE_EIGHTH 0x00000010 |

| #define ADC_CLOCK_SRC_PLL 0x00000000 |

| #define ADC_CLOCK_SRC_ALTCLK 0x00000001 |

| #define ADC_CLOCK_SRC_MOSC 0x00000002 |

| void ADCSampleRateSet | ( | uint32_t | ui32Base, |

| uint32_t | ui32ADCClock, | ||

| uint32_t | ui32Rate | ||

| ) |

| uint32_t ADCSampleRateGet | ( | uint32_t | ui32Base | ) |