|

|

|

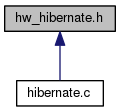

MSP432E4 DriverLib API Guide

1.11.00.03

|

Go to the source code of this file.

Macros | |

| #define | HIB_RTCC 0x400FC000 |

| #define | HIB_RTCM0 0x400FC004 |

| #define | HIB_RTCLD 0x400FC00C |

| #define | HIB_CTL 0x400FC010 |

| #define | HIB_IM 0x400FC014 |

| #define | HIB_RIS 0x400FC018 |

| #define | HIB_MIS 0x400FC01C |

| #define | HIB_IC 0x400FC020 |

| #define | HIB_RTCT 0x400FC024 |

| #define | HIB_RTCSS 0x400FC028 |

| #define | HIB_IO 0x400FC02C |

| #define | HIB_DATA 0x400FC030 |

| #define | HIB_CALCTL 0x400FC300 |

| #define | HIB_CAL0 0x400FC310 |

| #define | HIB_CAL1 0x400FC314 |

| #define | HIB_CALLD0 0x400FC320 |

| #define | HIB_CALLD1 0x400FC324 |

| #define | HIB_CALM0 0x400FC330 |

| #define | HIB_CALM1 0x400FC334 |

| #define | HIB_LOCK 0x400FC360 |

| #define | HIB_TPCTL 0x400FC400 |

| #define | HIB_TPSTAT 0x400FC404 |

| #define | HIB_TPIO 0x400FC410 |

| #define | HIB_TPLOG0 0x400FC4E0 |

| #define | HIB_TPLOG1 0x400FC4E4 |

| #define | HIB_TPLOG2 0x400FC4E8 |

| #define | HIB_TPLOG3 0x400FC4EC |

| #define | HIB_TPLOG4 0x400FC4F0 |

| #define | HIB_TPLOG5 0x400FC4F4 |

| #define | HIB_TPLOG6 0x400FC4F8 |

| #define | HIB_TPLOG7 0x400FC4FC |

| #define | HIB_PP 0x400FCFC0 |

| #define | HIB_CC 0x400FCFC8 |

| #define | HIB_RTCC_M 0xFFFFFFFF |

| #define | HIB_RTCC_S 0 |

| #define | HIB_RTCM0_M 0xFFFFFFFF |

| #define | HIB_RTCM0_S 0 |

| #define | HIB_RTCLD_M 0xFFFFFFFF |

| #define | HIB_RTCLD_S 0 |

| #define | HIB_CTL_WRC 0x80000000 |

| #define | HIB_CTL_RETCLR 0x40000000 |

| #define | HIB_CTL_OSCSEL 0x00080000 |

| #define | HIB_CTL_OSCDRV 0x00020000 |

| #define | HIB_CTL_OSCBYP 0x00010000 |

| #define | HIB_CTL_VBATSEL_M 0x00006000 |

| #define | HIB_CTL_VBATSEL_1_9V 0x00000000 |

| #define | HIB_CTL_VBATSEL_2_1V 0x00002000 |

| #define | HIB_CTL_VBATSEL_2_3V 0x00004000 |

| #define | HIB_CTL_VBATSEL_2_5V 0x00006000 |

| #define | HIB_CTL_BATCHK 0x00000400 |

| #define | HIB_CTL_BATWKEN 0x00000200 |

| #define | HIB_CTL_VDD3ON 0x00000100 |

| #define | HIB_CTL_VABORT 0x00000080 |

| #define | HIB_CTL_CLK32EN 0x00000040 |

| #define | HIB_CTL_PINWEN 0x00000010 |

| #define | HIB_CTL_RTCWEN 0x00000008 |

| #define | HIB_CTL_HIBREQ 0x00000002 |

| #define | HIB_CTL_RTCEN 0x00000001 |

| #define | HIB_IM_VDDFAIL 0x00000080 |

| #define | HIB_IM_RSTWK 0x00000040 |

| #define | HIB_IM_PADIOWK 0x00000020 |

| #define | HIB_IM_WC 0x00000010 |

| #define | HIB_IM_EXTW 0x00000008 |

| #define | HIB_IM_LOWBAT 0x00000004 |

| #define | HIB_IM_RTCALT0 0x00000001 |

| #define | HIB_RIS_VDDFAIL 0x00000080 |

| #define | HIB_RIS_RSTWK 0x00000040 |

| #define | HIB_RIS_PADIOWK 0x00000020 |

| #define | HIB_RIS_WC 0x00000010 |

| #define | HIB_RIS_EXTW 0x00000008 |

| #define | HIB_RIS_LOWBAT 0x00000004 |

| #define | HIB_RIS_RTCALT0 0x00000001 |

| #define | HIB_MIS_VDDFAIL 0x00000080 |

| #define | HIB_MIS_RSTWK 0x00000040 |

| #define | HIB_MIS_PADIOWK 0x00000020 |

| #define | HIB_MIS_WC 0x00000010 |

| #define | HIB_MIS_EXTW 0x00000008 |

| #define | HIB_MIS_LOWBAT 0x00000004 |

| #define | HIB_MIS_RTCALT0 0x00000001 |

| #define | HIB_IC_VDDFAIL 0x00000080 |

| #define | HIB_IC_RSTWK 0x00000040 |

| #define | HIB_IC_PADIOWK 0x00000020 |

| #define | HIB_IC_WC 0x00000010 |

| #define | HIB_IC_EXTW 0x00000008 |

| #define | HIB_IC_LOWBAT 0x00000004 |

| #define | HIB_IC_RTCALT0 0x00000001 |

| #define | HIB_RTCT_TRIM_M 0x0000FFFF |

| #define | HIB_RTCT_TRIM_S 0 |

| #define | HIB_RTCSS_RTCSSM_M 0x7FFF0000 |

| #define | HIB_RTCSS_RTCSSC_M 0x00007FFF |

| #define | HIB_RTCSS_RTCSSM_S 16 |

| #define | HIB_RTCSS_RTCSSC_S 0 |

| #define | HIB_IO_IOWRC 0x80000000 |

| #define | HIB_IO_WURSTEN 0x00000010 |

| #define | HIB_IO_WUUNLK 0x00000001 |

| #define | HIB_DATA_RTD_M 0xFFFFFFFF |

| #define | HIB_DATA_RTD_S 0 |

| #define | HIB_CALCTL_CAL24 0x00000004 |

| #define | HIB_CALCTL_CALEN 0x00000001 |

| #define | HIB_CAL0_VALID 0x80000000 |

| #define | HIB_CAL0_AMPM 0x00400000 |

| #define | HIB_CAL0_HR_M 0x001F0000 |

| #define | HIB_CAL0_MIN_M 0x00003F00 |

| #define | HIB_CAL0_SEC_M 0x0000003F |

| #define | HIB_CAL0_HR_S 16 |

| #define | HIB_CAL0_MIN_S 8 |

| #define | HIB_CAL0_SEC_S 0 |

| #define | HIB_CAL1_VALID 0x80000000 |

| #define | HIB_CAL1_DOW_M 0x07000000 |

| #define | HIB_CAL1_YEAR_M 0x007F0000 |

| #define | HIB_CAL1_MON_M 0x00000F00 |

| #define | HIB_CAL1_DOM_M 0x0000001F |

| #define | HIB_CAL1_DOW_S 24 |

| #define | HIB_CAL1_YEAR_S 16 |

| #define | HIB_CAL1_MON_S 8 |

| #define | HIB_CAL1_DOM_S 0 |

| #define | HIB_CALLD0_AMPM 0x00400000 |

| #define | HIB_CALLD0_HR_M 0x001F0000 |

| #define | HIB_CALLD0_MIN_M 0x00003F00 |

| #define | HIB_CALLD0_SEC_M 0x0000003F |

| #define | HIB_CALLD0_HR_S 16 |

| #define | HIB_CALLD0_MIN_S 8 |

| #define | HIB_CALLD0_SEC_S 0 |

| #define | HIB_CALLD1_DOW_M 0x07000000 |

| #define | HIB_CALLD1_YEAR_M 0x007F0000 |

| #define | HIB_CALLD1_MON_M 0x00000F00 |

| #define | HIB_CALLD1_DOM_M 0x0000001F |

| #define | HIB_CALLD1_DOW_S 24 |

| #define | HIB_CALLD1_YEAR_S 16 |

| #define | HIB_CALLD1_MON_S 8 |

| #define | HIB_CALLD1_DOM_S 0 |

| #define | HIB_CALM0_AMPM 0x00400000 |

| #define | HIB_CALM0_HR_M 0x001F0000 |

| #define | HIB_CALM0_MIN_M 0x00003F00 |

| #define | HIB_CALM0_SEC_M 0x0000003F |

| #define | HIB_CALM0_HR_S 16 |

| #define | HIB_CALM0_MIN_S 8 |

| #define | HIB_CALM0_SEC_S 0 |

| #define | HIB_CALM1_DOM_M 0x0000001F |

| #define | HIB_CALM1_DOM_S 0 |

| #define | HIB_LOCK_HIBLOCK_M 0xFFFFFFFF |

| #define | HIB_LOCK_HIBLOCK_KEY 0xA3359554 |

| #define | HIB_LOCK_HIBLOCK_S 0 |

| #define | HIB_TPCTL_WAKE 0x00000800 |

| #define | HIB_TPCTL_MEMCLR_M 0x00000300 |

| #define | HIB_TPCTL_MEMCLR_NONE 0x00000000 |

| #define | HIB_TPCTL_MEMCLR_LOW32 0x00000100 |

| #define | HIB_TPCTL_MEMCLR_HIGH32 0x00000200 |

| #define | HIB_TPCTL_MEMCLR_ALL 0x00000300 |

| #define | HIB_TPCTL_TPCLR 0x00000010 |

| #define | HIB_TPCTL_TPEN 0x00000001 |

| #define | HIB_TPSTAT_STATE_M 0x0000000C |

| #define | HIB_TPSTAT_STATE_DISABLED 0x00000000 |

| #define | HIB_TPSTAT_STATE_CONFIGED 0x00000004 |

| #define | HIB_TPSTAT_STATE_ERROR 0x00000008 |

| #define | HIB_TPSTAT_XOSCST 0x00000002 |

| #define | HIB_TPSTAT_XOSCFAIL 0x00000001 |

| #define | HIB_TPIO_GFLTR3 0x08000000 |

| #define | HIB_TPIO_PUEN3 0x04000000 |

| #define | HIB_TPIO_LEV3 0x02000000 |

| #define | HIB_TPIO_EN3 0x01000000 |

| #define | HIB_TPIO_GFLTR2 0x00080000 |

| #define | HIB_TPIO_PUEN2 0x00040000 |

| #define | HIB_TPIO_LEV2 0x00020000 |

| #define | HIB_TPIO_EN2 0x00010000 |

| #define | HIB_TPIO_GFLTR1 0x00000800 |

| #define | HIB_TPIO_PUEN1 0x00000400 |

| #define | HIB_TPIO_LEV1 0x00000200 |

| #define | HIB_TPIO_EN1 0x00000100 |

| #define | HIB_TPIO_GFLTR0 0x00000008 |

| #define | HIB_TPIO_PUEN0 0x00000004 |

| #define | HIB_TPIO_LEV0 0x00000002 |

| #define | HIB_TPIO_EN0 0x00000001 |

| #define | HIB_TPLOG0_TIME_M 0xFFFFFFFF |

| #define | HIB_TPLOG0_TIME_S 0 |

| #define | HIB_TPLOG1_XOSC 0x00010000 |

| #define | HIB_TPLOG1_TRIG3 0x00000008 |

| #define | HIB_TPLOG1_TRIG2 0x00000004 |

| #define | HIB_TPLOG1_TRIG1 0x00000002 |

| #define | HIB_TPLOG1_TRIG0 0x00000001 |

| #define | HIB_TPLOG2_TIME_M 0xFFFFFFFF |

| #define | HIB_TPLOG2_TIME_S 0 |

| #define | HIB_TPLOG3_XOSC 0x00010000 |

| #define | HIB_TPLOG3_TRIG3 0x00000008 |

| #define | HIB_TPLOG3_TRIG2 0x00000004 |

| #define | HIB_TPLOG3_TRIG1 0x00000002 |

| #define | HIB_TPLOG3_TRIG0 0x00000001 |

| #define | HIB_TPLOG4_TIME_M 0xFFFFFFFF |

| #define | HIB_TPLOG4_TIME_S 0 |

| #define | HIB_TPLOG5_XOSC 0x00010000 |

| #define | HIB_TPLOG5_TRIG3 0x00000008 |

| #define | HIB_TPLOG5_TRIG2 0x00000004 |

| #define | HIB_TPLOG5_TRIG1 0x00000002 |

| #define | HIB_TPLOG5_TRIG0 0x00000001 |

| #define | HIB_TPLOG6_TIME_M 0xFFFFFFFF |

| #define | HIB_TPLOG6_TIME_S 0 |

| #define | HIB_TPLOG7_XOSC 0x00010000 |

| #define | HIB_TPLOG7_TRIG3 0x00000008 |

| #define | HIB_TPLOG7_TRIG2 0x00000004 |

| #define | HIB_TPLOG7_TRIG1 0x00000002 |

| #define | HIB_TPLOG7_TRIG0 0x00000001 |

| #define | HIB_PP_TAMPER 0x00000002 |

| #define | HIB_PP_WAKENC 0x00000001 |

| #define | HIB_CC_SYSCLKEN 0x00000001 |

| #define HIB_RTCC 0x400FC000 |

Referenced by HibernateRTCGet().

| #define HIB_RTCM0 0x400FC004 |

Referenced by HibernateRTCMatchGet(), and HibernateRTCMatchSet().

| #define HIB_RTCLD 0x400FC00C |

| #define HIB_CTL 0x400FC010 |

Referenced by HibernateBatCheckDone(), HibernateBatCheckStart(), HibernateClockConfig(), HibernateDisable(), HibernateEnableExpClk(), HibernateGPIORetentionDisable(), HibernateGPIORetentionEnable(), HibernateGPIORetentionGet(), HibernateIsActive(), HibernateLowBatGet(), HibernateLowBatSet(), HibernateRequest(), HibernateRTCDisable(), HibernateRTCEnable(), HibernateWakeGet(), and HibernateWakeSet().

| #define HIB_IM 0x400FC014 |

Referenced by HibernateIntDisable(), and HibernateIntEnable().

| #define HIB_RIS 0x400FC018 |

Referenced by HibernateIntStatus().

| #define HIB_MIS 0x400FC01C |

Referenced by HibernateIntStatus().

| #define HIB_IC 0x400FC020 |

Referenced by HibernateIntClear().

| #define HIB_RTCT 0x400FC024 |

Referenced by HibernateRTCTrimGet(), and HibernateRTCTrimSet().

| #define HIB_RTCSS 0x400FC028 |

Referenced by HibernateRTCSSGet(), HibernateRTCSSMatchGet(), and HibernateRTCSSMatchSet().

| #define HIB_IO 0x400FC02C |

Referenced by HibernateWakeGet().

| #define HIB_DATA 0x400FC030 |

Referenced by HibernateDataGet(), and HibernateDataSet().

| #define HIB_CALCTL 0x400FC300 |

Referenced by HibernateCalendarGet(), HibernateCalendarMatchGet(), HibernateCounterMode(), and HibernateTamperEventsGet().

| #define HIB_CAL0 0x400FC310 |

Referenced by HibernateCalendarGet(), and HibernateTamperEventsGet().

| #define HIB_CAL1 0x400FC314 |

Referenced by HibernateCalendarGet().

| #define HIB_CALLD0 0x400FC320 |

| #define HIB_CALLD1 0x400FC324 |

| #define HIB_CALM0 0x400FC330 |

Referenced by HibernateCalendarMatchGet().

| #define HIB_CALM1 0x400FC334 |

Referenced by HibernateCalendarMatchGet().

| #define HIB_LOCK 0x400FC360 |

| #define HIB_TPCTL 0x400FC400 |

Referenced by HibernateTamperEventsConfig().

| #define HIB_TPSTAT 0x400FC404 |

Referenced by HibernateTamperStatusGet().

| #define HIB_TPIO 0x400FC410 |

Referenced by HibernateTamperIOEnable().

| #define HIB_TPLOG0 0x400FC4E0 |

Referenced by HibernateTamperEventsGet().

| #define HIB_TPLOG1 0x400FC4E4 |

| #define HIB_TPLOG2 0x400FC4E8 |

| #define HIB_TPLOG3 0x400FC4EC |

| #define HIB_TPLOG4 0x400FC4F0 |

| #define HIB_TPLOG5 0x400FC4F4 |

| #define HIB_TPLOG6 0x400FC4F8 |

| #define HIB_TPLOG7 0x400FC4FC |

| #define HIB_PP 0x400FCFC0 |

| #define HIB_CC 0x400FCFC8 |

| #define HIB_RTCC_M 0xFFFFFFFF |

| #define HIB_RTCC_S 0 |

| #define HIB_RTCM0_M 0xFFFFFFFF |

| #define HIB_RTCM0_S 0 |

| #define HIB_RTCLD_M 0xFFFFFFFF |

| #define HIB_RTCLD_S 0 |

| #define HIB_CTL_WRC 0x80000000 |

| #define HIB_CTL_RETCLR 0x40000000 |

Referenced by HibernateGPIORetentionDisable(), HibernateGPIORetentionEnable(), and HibernateGPIORetentionGet().

| #define HIB_CTL_OSCSEL 0x00080000 |

| #define HIB_CTL_OSCDRV 0x00020000 |

| #define HIB_CTL_OSCBYP 0x00010000 |

| #define HIB_CTL_VBATSEL_M 0x00006000 |

Referenced by HibernateLowBatGet(), and HibernateLowBatSet().

| #define HIB_CTL_VBATSEL_1_9V 0x00000000 |

| #define HIB_CTL_VBATSEL_2_1V 0x00002000 |

| #define HIB_CTL_VBATSEL_2_3V 0x00004000 |

| #define HIB_CTL_VBATSEL_2_5V 0x00006000 |

| #define HIB_CTL_BATCHK 0x00000400 |

Referenced by HibernateBatCheckDone(), and HibernateBatCheckStart().

| #define HIB_CTL_BATWKEN 0x00000200 |

| #define HIB_CTL_VDD3ON 0x00000100 |

Referenced by HibernateGPIORetentionDisable(), HibernateGPIORetentionEnable(), and HibernateGPIORetentionGet().

| #define HIB_CTL_VABORT 0x00000080 |

| #define HIB_CTL_CLK32EN 0x00000040 |

Referenced by HibernateClockConfig(), HibernateDisable(), HibernateEnableExpClk(), and HibernateIsActive().

| #define HIB_CTL_PINWEN 0x00000010 |

| #define HIB_CTL_RTCWEN 0x00000008 |

| #define HIB_CTL_HIBREQ 0x00000002 |

Referenced by HibernateRequest().

| #define HIB_CTL_RTCEN 0x00000001 |

Referenced by HibernateRTCDisable(), and HibernateRTCEnable().

| #define HIB_IM_VDDFAIL 0x00000080 |

| #define HIB_IM_RSTWK 0x00000040 |

| #define HIB_IM_PADIOWK 0x00000020 |

| #define HIB_IM_WC 0x00000010 |

| #define HIB_IM_EXTW 0x00000008 |

| #define HIB_IM_LOWBAT 0x00000004 |

| #define HIB_IM_RTCALT0 0x00000001 |

| #define HIB_RIS_VDDFAIL 0x00000080 |

| #define HIB_RIS_RSTWK 0x00000040 |

| #define HIB_RIS_PADIOWK 0x00000020 |

| #define HIB_RIS_WC 0x00000010 |

| #define HIB_RIS_EXTW 0x00000008 |

| #define HIB_RIS_LOWBAT 0x00000004 |

| #define HIB_RIS_RTCALT0 0x00000001 |

| #define HIB_MIS_VDDFAIL 0x00000080 |

| #define HIB_MIS_RSTWK 0x00000040 |

| #define HIB_MIS_PADIOWK 0x00000020 |

| #define HIB_MIS_WC 0x00000010 |

| #define HIB_MIS_EXTW 0x00000008 |

| #define HIB_MIS_LOWBAT 0x00000004 |

| #define HIB_MIS_RTCALT0 0x00000001 |

| #define HIB_IC_VDDFAIL 0x00000080 |

| #define HIB_IC_RSTWK 0x00000040 |

| #define HIB_IC_PADIOWK 0x00000020 |

| #define HIB_IC_WC 0x00000010 |

| #define HIB_IC_EXTW 0x00000008 |

| #define HIB_IC_LOWBAT 0x00000004 |

| #define HIB_IC_RTCALT0 0x00000001 |

| #define HIB_RTCT_TRIM_M 0x0000FFFF |

| #define HIB_RTCT_TRIM_S 0 |

| #define HIB_RTCSS_RTCSSM_M 0x7FFF0000 |

| #define HIB_RTCSS_RTCSSC_M 0x00007FFF |

Referenced by HibernateRTCSSGet().

| #define HIB_RTCSS_RTCSSM_S 16 |

Referenced by HibernateRTCSSMatchGet(), and HibernateRTCSSMatchSet().

| #define HIB_RTCSS_RTCSSC_S 0 |

| #define HIB_IO_IOWRC 0x80000000 |

| #define HIB_IO_WURSTEN 0x00000010 |

| #define HIB_IO_WUUNLK 0x00000001 |

| #define HIB_DATA_RTD_M 0xFFFFFFFF |

| #define HIB_DATA_RTD_S 0 |

| #define HIB_CALCTL_CAL24 0x00000004 |

Referenced by HibernateCalendarGet(), HibernateCalendarMatchGet(), and HibernateTamperEventsGet().

| #define HIB_CALCTL_CALEN 0x00000001 |

Referenced by HibernateCalendarGet(), HibernateCalendarMatchGet(), and HibernateTamperEventsGet().

| #define HIB_CAL0_VALID 0x80000000 |

Referenced by HibernateCalendarGet().

| #define HIB_CAL0_AMPM 0x00400000 |

Referenced by HibernateCalendarGet(), HibernateCalendarMatchGet(), and HibernateTamperEventsGet().

| #define HIB_CAL0_HR_M 0x001F0000 |

Referenced by HibernateCalendarGet(), and HibernateCalendarMatchGet().

| #define HIB_CAL0_MIN_M 0x00003F00 |

Referenced by HibernateCalendarGet(), and HibernateCalendarMatchGet().

| #define HIB_CAL0_SEC_M 0x0000003F |

Referenced by HibernateCalendarGet(), and HibernateCalendarMatchGet().

| #define HIB_CAL0_HR_S 16 |

Referenced by HibernateCalendarGet(), and HibernateCalendarMatchGet().

| #define HIB_CAL0_MIN_S 8 |

Referenced by HibernateCalendarGet(), and HibernateCalendarMatchGet().

| #define HIB_CAL0_SEC_S 0 |

Referenced by HibernateCalendarGet(), and HibernateCalendarMatchGet().

| #define HIB_CAL1_VALID 0x80000000 |

Referenced by HibernateCalendarGet().

| #define HIB_CAL1_DOW_M 0x07000000 |

Referenced by HibernateCalendarGet().

| #define HIB_CAL1_YEAR_M 0x007F0000 |

Referenced by HibernateCalendarGet().

| #define HIB_CAL1_MON_M 0x00000F00 |

Referenced by HibernateCalendarGet().

| #define HIB_CAL1_DOM_M 0x0000001F |

Referenced by HibernateCalendarGet(), and HibernateCalendarMatchGet().

| #define HIB_CAL1_DOW_S 24 |

Referenced by HibernateCalendarGet().

| #define HIB_CAL1_YEAR_S 16 |

Referenced by HibernateCalendarGet().

| #define HIB_CAL1_MON_S 8 |

Referenced by HibernateCalendarGet().

| #define HIB_CAL1_DOM_S 0 |

Referenced by HibernateCalendarGet(), and HibernateCalendarMatchGet().

| #define HIB_CALLD0_AMPM 0x00400000 |

| #define HIB_CALLD0_HR_M 0x001F0000 |

| #define HIB_CALLD0_MIN_M 0x00003F00 |

| #define HIB_CALLD0_SEC_M 0x0000003F |

| #define HIB_CALLD0_HR_S 16 |

| #define HIB_CALLD0_MIN_S 8 |

| #define HIB_CALLD0_SEC_S 0 |

| #define HIB_CALLD1_DOW_M 0x07000000 |

| #define HIB_CALLD1_YEAR_M 0x007F0000 |

| #define HIB_CALLD1_MON_M 0x00000F00 |

| #define HIB_CALLD1_DOM_M 0x0000001F |

| #define HIB_CALLD1_DOW_S 24 |

| #define HIB_CALLD1_YEAR_S 16 |

| #define HIB_CALLD1_MON_S 8 |

| #define HIB_CALLD1_DOM_S 0 |

| #define HIB_CALM0_AMPM 0x00400000 |

| #define HIB_CALM0_HR_M 0x001F0000 |

| #define HIB_CALM0_MIN_M 0x00003F00 |

| #define HIB_CALM0_SEC_M 0x0000003F |

| #define HIB_CALM0_HR_S 16 |

| #define HIB_CALM0_MIN_S 8 |

| #define HIB_CALM0_SEC_S 0 |

| #define HIB_CALM1_DOM_M 0x0000001F |

| #define HIB_CALM1_DOM_S 0 |

| #define HIB_LOCK_HIBLOCK_M 0xFFFFFFFF |

| #define HIB_LOCK_HIBLOCK_KEY 0xA3359554 |

| #define HIB_LOCK_HIBLOCK_S 0 |

| #define HIB_TPCTL_WAKE 0x00000800 |

| #define HIB_TPCTL_MEMCLR_M 0x00000300 |

Referenced by HibernateTamperEventsConfig().

| #define HIB_TPCTL_MEMCLR_NONE 0x00000000 |

| #define HIB_TPCTL_MEMCLR_LOW32 0x00000100 |

| #define HIB_TPCTL_MEMCLR_HIGH32 0x00000200 |

| #define HIB_TPCTL_MEMCLR_ALL 0x00000300 |

| #define HIB_TPCTL_TPCLR 0x00000010 |

| #define HIB_TPCTL_TPEN 0x00000001 |

| #define HIB_TPSTAT_STATE_M 0x0000000C |

Referenced by HibernateTamperStatusGet().

| #define HIB_TPSTAT_STATE_DISABLED 0x00000000 |

| #define HIB_TPSTAT_STATE_CONFIGED 0x00000004 |

| #define HIB_TPSTAT_STATE_ERROR 0x00000008 |

| #define HIB_TPSTAT_XOSCST 0x00000002 |

Referenced by HibernateTamperStatusGet().

| #define HIB_TPSTAT_XOSCFAIL 0x00000001 |

Referenced by HibernateTamperStatusGet().

| #define HIB_TPIO_GFLTR3 0x08000000 |

| #define HIB_TPIO_PUEN3 0x04000000 |

| #define HIB_TPIO_LEV3 0x02000000 |

| #define HIB_TPIO_EN3 0x01000000 |

| #define HIB_TPIO_GFLTR2 0x00080000 |

| #define HIB_TPIO_PUEN2 0x00040000 |

| #define HIB_TPIO_LEV2 0x00020000 |

| #define HIB_TPIO_EN2 0x00010000 |

| #define HIB_TPIO_GFLTR1 0x00000800 |

| #define HIB_TPIO_PUEN1 0x00000400 |

| #define HIB_TPIO_LEV1 0x00000200 |

| #define HIB_TPIO_EN1 0x00000100 |

| #define HIB_TPIO_GFLTR0 0x00000008 |

Referenced by HibernateTamperIOEnable().

| #define HIB_TPIO_PUEN0 0x00000004 |

Referenced by HibernateTamperIOEnable().

| #define HIB_TPIO_LEV0 0x00000002 |

Referenced by HibernateTamperIOEnable().

| #define HIB_TPIO_EN0 0x00000001 |

Referenced by HibernateTamperIOEnable().

| #define HIB_TPLOG0_TIME_M 0xFFFFFFFF |

| #define HIB_TPLOG0_TIME_S 0 |

| #define HIB_TPLOG1_XOSC 0x00010000 |

| #define HIB_TPLOG1_TRIG3 0x00000008 |

| #define HIB_TPLOG1_TRIG2 0x00000004 |

| #define HIB_TPLOG1_TRIG1 0x00000002 |

| #define HIB_TPLOG1_TRIG0 0x00000001 |

| #define HIB_TPLOG2_TIME_M 0xFFFFFFFF |

| #define HIB_TPLOG2_TIME_S 0 |

| #define HIB_TPLOG3_XOSC 0x00010000 |

| #define HIB_TPLOG3_TRIG3 0x00000008 |

| #define HIB_TPLOG3_TRIG2 0x00000004 |

| #define HIB_TPLOG3_TRIG1 0x00000002 |

| #define HIB_TPLOG3_TRIG0 0x00000001 |

| #define HIB_TPLOG4_TIME_M 0xFFFFFFFF |

| #define HIB_TPLOG4_TIME_S 0 |

| #define HIB_TPLOG5_XOSC 0x00010000 |

| #define HIB_TPLOG5_TRIG3 0x00000008 |

| #define HIB_TPLOG5_TRIG2 0x00000004 |

| #define HIB_TPLOG5_TRIG1 0x00000002 |

| #define HIB_TPLOG5_TRIG0 0x00000001 |

| #define HIB_TPLOG6_TIME_M 0xFFFFFFFF |

| #define HIB_TPLOG6_TIME_S 0 |

| #define HIB_TPLOG7_XOSC 0x00010000 |

| #define HIB_TPLOG7_TRIG3 0x00000008 |

| #define HIB_TPLOG7_TRIG2 0x00000004 |

| #define HIB_TPLOG7_TRIG1 0x00000002 |

| #define HIB_TPLOG7_TRIG0 0x00000001 |

| #define HIB_PP_TAMPER 0x00000002 |

| #define HIB_PP_WAKENC 0x00000001 |

| #define HIB_CC_SYSCLKEN 0x00000001 |